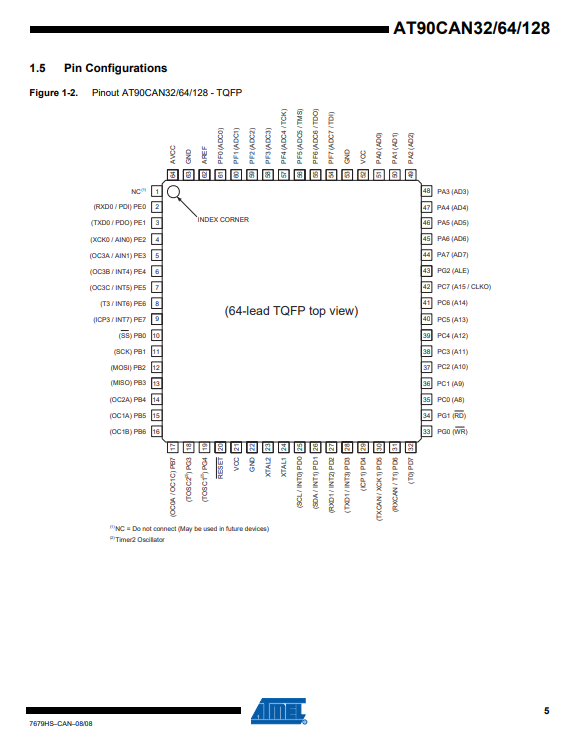

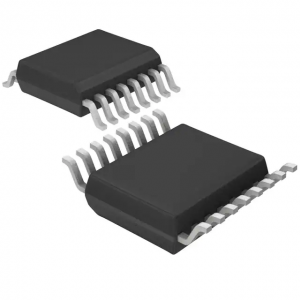

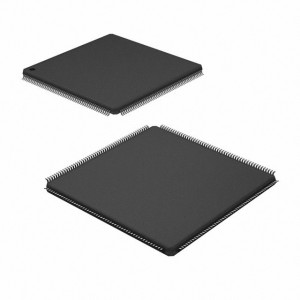

AT90CAN128-16AU IC MCU 8BIT 128KB FLASH 64TQFP

Product Parameter

Descriptio

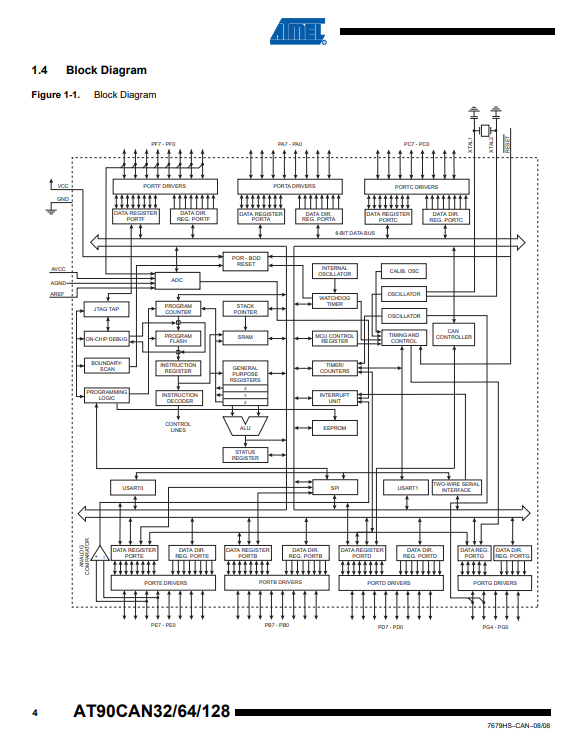

AT90CAN32/64/128 humilis potentia est CMOS 8-bit microcontroller ex architectura AVR aucta RISC.Exsequendo instructiones potentes in unius cycli horologii, AT90CAN32/64/128 perquirit per putationes appropinquantes 1 MIPS per MHz permittens systema excogitatoris ad potentiae consummationem versus processui celeritatem.In AVR nucleus uberem componit instructionem cum 32 propositi generalis registris operandis.Omnes 32 registrae directe connectuntur cum Unit Arithmetica Logica (ALU), duo regestra independentes accesserunt in una instructione in uno cyclo horologii exsecuto.Architectura consequens magis signum efficax est dum perputs assequendum decies velocius est quam CISC microcontrollers conventionalis.AT90CAN32/64/128 sequentes lineamenta praebet: 32K/64K/128K bytes of In-System Programmabilis Mico cum Read-Dum-Scribe facultates, 1K/2K/4K bytes EEPROM, 2K/4K/4K bytes SRAM, 53 propositi generalis I/O lineae, 32 propositi generalis tabulae operandi, moderator potest, Tempus Verus Counter (RTC), quattuor flexibiles Timer/Cunters cum modis comparantibus et PWM, 2 USARTs, a byte ordinantur duae filum Serial interface, 8-alveum 10 -bit ADC cum sceno differentiali initus libitum cum lucro programmabili, programmabile Watchdog Timer cum Oscillatore Interno, SPI Vide portum, IEEE std.1149.1 facilis JTAG test interface, etiam usus est ad accessionem systema-chip Debug et programmandi et quinque programmatum selectabilium potentiarum salutarium modorum.Modus otiosus CPU sistit dum SRAM, Timer/Calculas, SPI/CAN portus permittens et systema interrumpendi ad operationem perdurandi.Modus Power-down conservat actis mandare sed Oscillatorem coit, inactivare omnia alia munera chippis usque ad proximam interrumpendam vel Reset Hardware.In Potentia-salva modo, timer asynchronus currere pergit, sino utentem ad basin timer conservandam dum reliqui machini dormiunt.Sonitus reductionis ADC modus sistit CPU et omnes moduli I/O praeter Timer Asynchronum et ADC, ad magnas commutationes ADC mutandi strepitus.In mode standby, Crystal/Resonator Oscillator currit dum reliquae machinae dormiunt.Hoc satus-usque ieiunium cum humili potentia consummatio concedit.Fabrica fabricata est usus summus densitatis Atmel technologiae memoriae nonvolatilis.Onchip ISP Flash permittit memoriam programmatis reprogrammed in systemate SPI Vide interfaciem, per programmatorem memoriae non volatile conventionale, vel per programmatum sclopeticum Boot in AVR core currentem.Programma tabernus quodvis interface uti potest ad applicationem programmatis applicationis in applicatione Mico memoria comprehendere.Software in Boot Flash section perget currere dum Sectio Mico Applicationis renovatur, dum operatio vera Read-Write.

| Formularium: | |

| attributum | Precium |

| Categoria | Integrated Circuitus (IC) |

| Embedded - Microcontrollers | |

| Mfr | Microchip Technology |

| Series | AVR® 90CAN |

| sarcina | Tray |

| Pars Status | Active |

| Core Processor | AVR |

| Core Size | 8-Bit |

| Celeritas | 16MHz |

| Connectivity | CANbus, EBI/EMI, I²C, SPI, UART/USART . |

| Peripherales | Brown-out Detect/Reset, POR, PWM, WDT |

| Numerus I / O * | 53 |

| Programma Memoria Location | 128KB (128K x 8) |

| Programma Memoria Type | FULGEO |

| EEPROM Location | 4K x 8 |

| RAM Location | 4K x 8 |

| Voltage - Supple (Vcc/Vdd) | 2.7V ~ 5.5V |

| Data Converters | A/D 8x10b |

| Oscillator Type | Internum |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Adscendens Type | Superficie montis |

| Sarcina / Case | 64-TQFP |

| Elit Fabrica Package | 64-TQFP (14x14) |

| Basis Product Number | AT90CAN128 |

RelatedPRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp