ATTINY24A-SSUR IC MCU 8BIT 2KB FLASH 14SOIC

Product Parameter

Descriptio

ATtiny24A/44A/84A potentiae humiles CMOS 8-bit microcontrollers ex AVR architectura RISC aucta sunt.Potentes instructiones in unius cycli horologii exequendo, ATtiny24A/44A/84A per putes accedens 1 MIPS per MHz permittit ratio excogitatoris ad optimize potentiae consummationem versus processus celeritatem.In AVR nucleus uberem componit instructionem cum 32 propositi generalis registris operandis.Omnes 32 registrae directe connectuntur cum Unit Arithmetica Logica (ALU), duo regestra independentes accesserunt in una instructione in uno cyclo horologii exsecuto.Architectura consequens magis signum efficax est dum perputs assequendum decies velocius est quam CISC microcontrollers conventionalis.ATtiny24A/44A/84A The ATtiny24A/44A/84A sequentes notas praebet: 2K/4K/8K byte de In-System Programmabili Flash, 128/256/512 bytes EEPROM, 128/256/512 bytes SRAM, 12 propositi generalis I/ O lineae, 32 propositi generalis tabulae operandi, in 8-bit Timer/Contra cum duobus canalibus PWM, a 16 frenum timer/contro cum duobus canalibus PWM, Internis et Externis Interruptis, a 8-alveum 10-bit ADC, programmabilem scaenam. (1x, 20x) pro 12 binis canalis differentialis ADC, speculativus Timer speculator cum oscillatore interno, oscillator calibratus internus, et quattuor programmata selectabilia potentiae salvificae modi.Modus otiosus CPU sistit dum SRAM, Timer/Contro, ADC, Analog Comparator obsistit, et systema continuandi muneris interrumpit.ADC Noise Reductio modus minimizes mutandi strepitus in conversionibus ADC, intercipiendo CPU et omnes I/O modulorum praeter ADC.In registris Power-down modus contenta sua custodiunt et omnia functiones chippis debilitantur usque ad proximam interrumpendam vel ferrariam reset.In modo standby, oscillator crystallus/resonator currit dum reliqua technicae machinae dormiunt, initium velocissimum permittens cum humilitate potentiae consummationis coniunctum.Fabrica fabricatur per densitatem altam Atmel densitatis memoriae technologiae non-volatilis.Onchip ISP Flash permittit memoriam Programma re-programma in systemate SPI Vide interface, per programmatorem memoriae non volatile conventionale vel per codicillos codici currens in AVR core.ATtiny24A/44A/84A AVR plena consentanea programmatis et systematis instrumentorum evolutionis sustentatur inter quas: C Compilatores, Macro Congregatores, Programma Debugger/simulatores et Aestimatio kits.

| Formularium: | |

| attributum | Precium |

| Categoria | Integrated Circuitus (IC) |

| Embedded - Microcontrollers | |

| Mfr | Microchip Technology |

| Series | AVR® ATtiny |

| sarcina | Tubus |

| Pars Status | Active |

| Core Processor | AVR |

| Core Size | 8-Bit |

| Celeritas | 20MHz |

| Connectivity | USI' |

| Peripherales | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT |

| Numerus I / O * | 12 |

| Programma Memoria Location | 2KB (1K x 16) |

| Programma Memoria Type | FULGEO |

| EEPROM Location | 128 x 8 |

| RAM Location | 128 x 8 |

| Voltage - Supple (Vcc/Vdd) | 1.8V ~ 5.5V |

| Data Converters | A/D 8x10b |

| Oscillator Type | Internum |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Adscendens Type | Superficie montis |

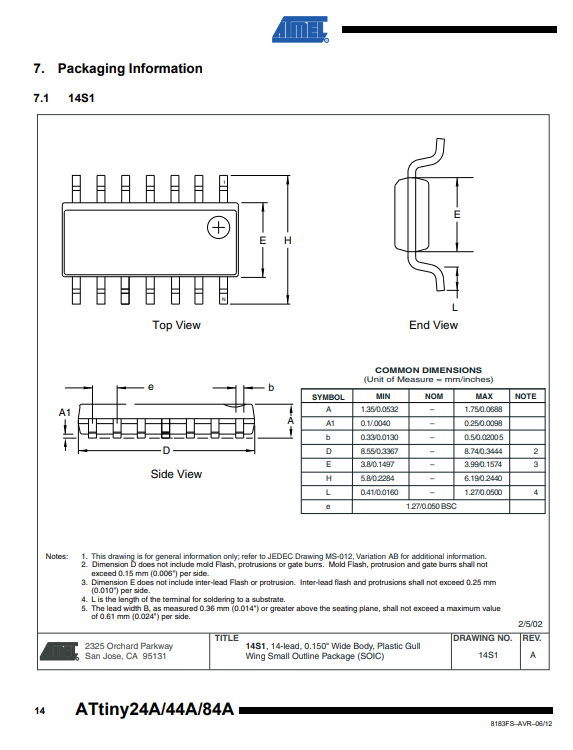

| Sarcina / Case | 14-SOIC (0.154", 3.90mm Latitudo) |

| Elit Fabrica Package | 14-SOIC |

| Basis Product Number | ATTINY24 |

RelatedPRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp