ATXMEGA256C3-AUR IC MCU 8/16BIT 256KB FLSH 64TQFP

Product Parameter

Descriptio

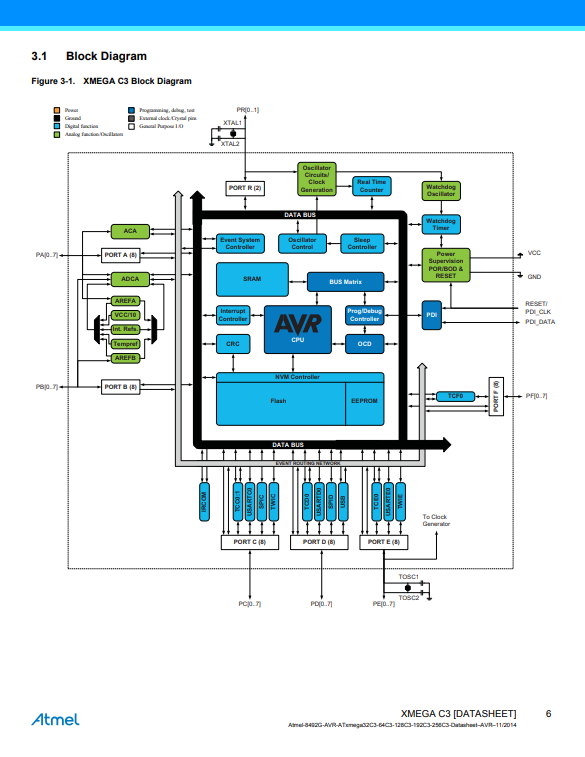

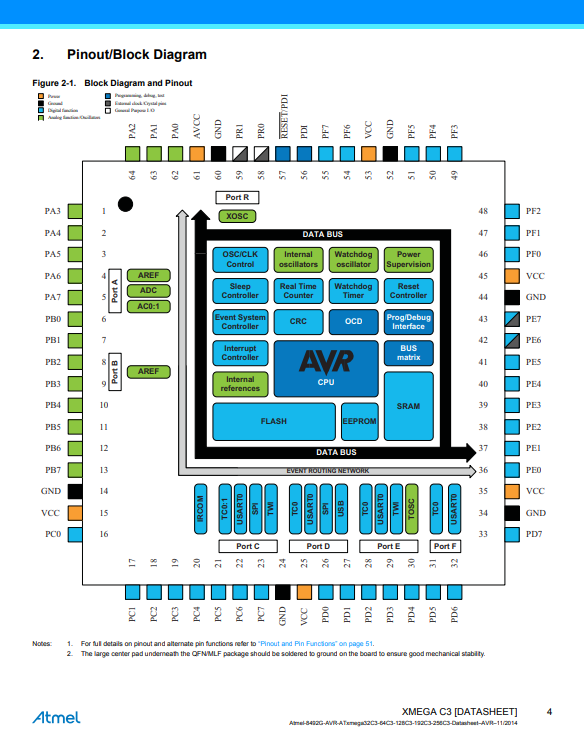

The Atmel AVR XMEGA familia est potentiae humilis, magnae operationis, et locupletium peripheralium 8/16-bitrum microcontrollorum qui ab AVR architectura RISC auctus est.Exsequendo instructiones in unius cycli horologii, cogitationes AVR XMEGA consequi CPU perput accedens una decies instructiones per megahertz secundo (MIPS) per megahertz, permittens systema excogitatoris ad optimize potentiae consummationem versus celeritatem processus expediendi.AVR CPU uberem instructionem cum 32 propositis libris operantibus generatim coniungit.Omnes libri 32 registrae ad arithmeticam logicam unitatem directe connexae sunt, permittens duo regestra independentia accessere in una instructione, in uno cyclo horologii exsecuti.Architectura consequens plus codicis efficiens est, dum perputs multoties velocius assequatur, quam conventionales unius accumulator vel CISC microcontrollers fundantur.XMEGA C3 machinas sequentes notas praebent: in systematis programmabilis mico cum facultates scribendo scribe;internus EEPROM et SRAM;quattuor trames eventus systematis et programmabilis multilevel interrumpunt moderatorem, 50 propositum generale I/O lineae, 16 frenum real-time counter (RTC);quinque, 16-bit timer/calculis cum canalibus compara et PWM;tres USARTs;duo filum vide interfaces (TWIs);unus cursu pleno USB 2.0 interface;two serial interfaces peripherales (SPIS);unum alveum sedecim, 12 frenum ADC cum lucro programmabili;duo analogon comparatores (ACs) cum fenestra modus;timer programmabilis speculator oscillator internus separatus;accurate oscillatores interni cum PLL et prescalibus;and programmable brown-out deprehensio.Propositum et debug interface (PDI), ieiunium, duo clavum interfaciendi ad programmandi et debugging, praesto est.In XMEGA C3 machinis quinque programmatibus selectabiles potentiae salutaris modos habent.Modus otiosus CPU impedit dum SRAM, eventus systematis, moderatorem interrumpunt, omnesque peripherales operandi continuandi.Modus potentia-down SRAM servat et actis mandare contenta, sed oscillatores sistit, omnes alias functiones inactivare usque ad proximum TWI, USB resumere, vel clavum mutationem interrumpere, vel retexere.In potestate praeter modum, asynchronum temporis realis tempus currere pergit, sino applicatione ad basim timoris conservandam dum reliquae machinae dormiunt.In modo sto, oscillator externus cristallus currit dum reliqua technologia dormit.Hoc satus a crystallo externo permittit velocissimus, cum humilis potentia consummatio.In modum extenso, praecipuus oscillator tum timor asynchronus decurrunt.Ad vim consummationem ulterius reducendam, horologium periphericum unicuique periphericum optione obstrui potest in modo activo et otioso somni modo.

| Formularium: | |

| attributum | Precium |

| Categoria | Integrated Circuitus (IC) |

| Embedded - Microcontrollers | |

| Mfr | Microchip Technology |

| Series | AVR® XMEGA® C3 |

| sarcina | Tape & Reel (TR) |

| Cut Tape (CT) | |

| Digi-Reel® | |

| Pars Status | Active |

| Core Processor | AVR |

| Core Size | 8/16-Bit |

| Celeritas | 32MHz |

| Connectivity | I²C, IrDA, SPI, UART/USART, USB |

| Peripherales | Brown-out Detect/Reset, DMA, POR, PWM, WDT |

| Numerus I / O * | 50 |

| Programma Memoria Location | 256KB (128K x 16) |

| Programma Memoria Type | FULGEO |

| EEPROM Location | 4K x 8 |

| RAM Location | 16K x 8 |

| Voltage - Supple (Vcc/Vdd) | 1.6V ~ 3.6V |

| Data Converters | A/D 16x12b |

| Oscillator Type | Internum |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Adscendens Type | Superficie montis |

| Sarcina / Case | 64-TQFP |

| Elit Fabrica Package | 64-TQFP (14x14) |

| Basis Product Number | ATXMEGA256 |

RelatedPRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp