MC9S12XET256MAL IC MCU 16BIT 256KB FLASH 112LQFP

Product Parameter

Descriptio

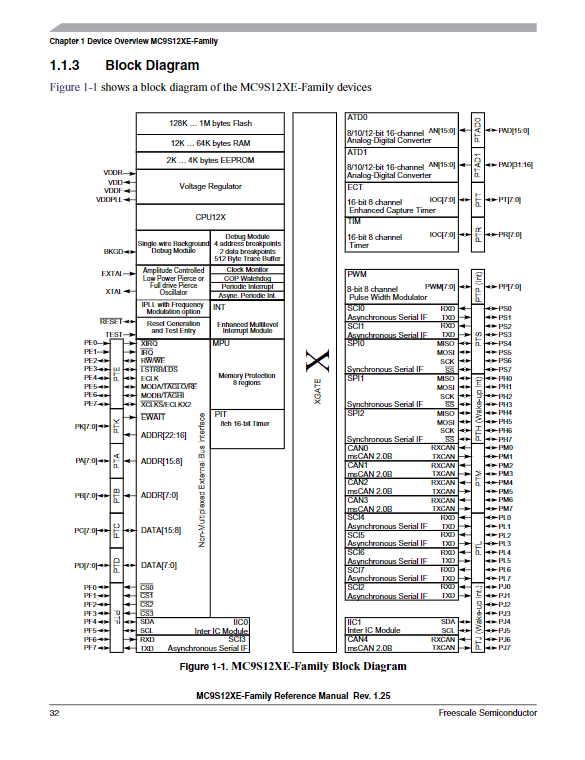

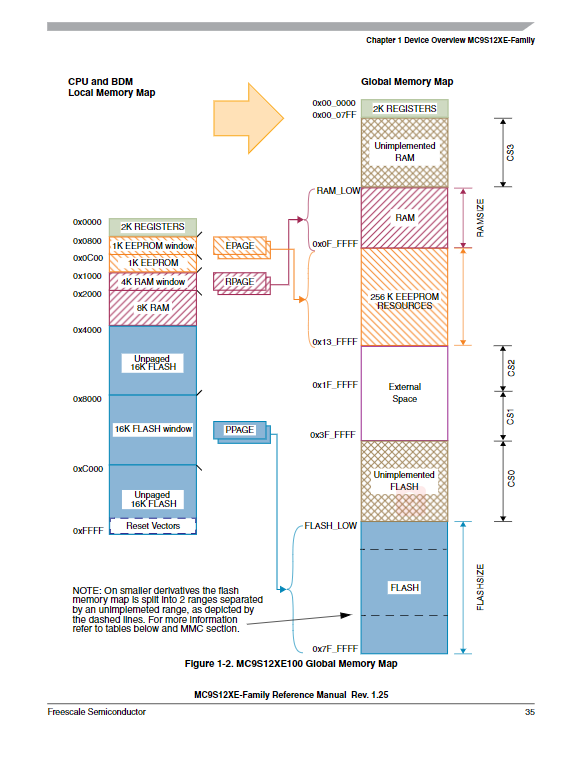

MC9S12XE-Familia moderatorum microform est ulterior progressus in S12XD-Familiae notis novis inclusis ad integritatem systematis aucti et maioris functionis.Hae novae notae includunt aMemory Protection Unit (MPU) et Error Correctio Codicis (ECC) in memoria Flash cum aucta functione EEPROM (EEE), aucta XGATE, interna percolata, frequentia Phase Locked Loop (IPLL) et aucta ATD.E-Familia S12X producta extendit usque ad 1MB memoriae Flash cum auctis I/O facultatem in 208 clavo versionis praetoriae MC9S12XE100. Familia MC9S12XE-Familia 32 frenum tradit effectum cum omnibus commodis et efficacibus 16 bitMCU.Sumptus humilis, consumptio potentiae retinet, EMC et codici amplitudo commoda efficientiae quae nunc gaudent ab utentibus Freescale existentis 16-Bit MC9S12 et S12X MCU familias.Excelsa planities est ofcompatibilitatis inter familias S12XE et S12XD. Familia MC9S12XE-familiae notat auctam versionem co-processionis faciendi boosting XGATE qui programmabilis est in lingua "C" et in bis currit frequentia S12X cum aninstructione statuto optimized ad notitias motus, logicas et manipulationes instructiones frenum et quae moduli peripherici in fabrica possunt inservire.Nova versio aucta emendavit tractandi facultatem interrumpere et plene compatitur cum XGATE moduli exsistenti. Familia MC9S12XE-Familia composita est ex vexillum periphericum in chip, in quibus usque ad 64Kbytes de RAM, octo asynchronae Vide interfaces communicationum (SCI), tres interfaces peripherales seriales (SPI), canalis 8 IC/OC timoris captis auctus (ECT), duo 16-alvei, 12 frenum analogum ad digitales conversis, 8 canalis pulsus-latitudo modulator (PWM), quinque CAN 2.0 A; B programmatio moduli compatibilis (MSCAN12), duo inter-IC bus caudices (IIC), 8-alveus 24 frenum periodicum timer interrumpunt (PIT) et 8 alveum 16-bitstandardi timoris moduli (TIM).The MC9S12XE-Family usus 16-bit accessus amplus sine insidiis civitatibus pro omnibus periphericis et memoriis. In non-multiplexis dilatatis bus instrumenti in promptu sunt versiones 144/208-pin permittit facilem interfacies ad memoriam externam. Praeter I/O portus in singulis modulis praesto, usque ad XXVI amplius I / O portus sunt praesto cum interruptcapability almugientes Wake-Up ab STOP vel EXSPECTATIO modi.In MC9S12XE-Familia praesto est in 208-PIN MAPBGA, 144-pin LQFP, 112-pin LQFP vel 80-pin QFP bene.

| Formularium: | |

| attributum | Precium |

| Categoria | Integrated Circuitus (IC) |

| Embedded - Microcontrollers | |

| Mfr | NXP USA Inc. |

| Series | HCS12X |

| sarcina | Tray |

| Pars Status | Active |

| Core Processor | HCS12X |

| Core Size | 16-Bit |

| Celeritas | 50MHz |

| Connectivity | CANbus, EBI/EMI, I²C, IrDA, SCI, SPI . |

| Peripherales | LVD, POR, PWM, WDT |

| Numerus I / O * | 91 |

| Programma Memoria Location | 256KB (256K x 8) |

| Programma Memoria Type | FULGEO |

| EEPROM Location | 4K x 8 |

| RAM Location | 16K x 8 |

| Voltage - Supple (Vcc/Vdd) | 1.72V ~ 5.5V |

| Data Converters | A/D 12x12b |

| Oscillator Type | Externum |

| Operating Temperature | -40°C ~ 125°C (TA) |

| Adscendens Type | Superficie montis |

| Sarcina / Case | 112-LQFP |

| Elit Fabrica Package | 112-LQFP (20x20) |

| Basis Product Number | MC9S12 |

RelatedPRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp