TMS320C6657CZHA IC DSP FIX/FLOAT proceditur 625FCBGA

Product Parameter

Descriptio

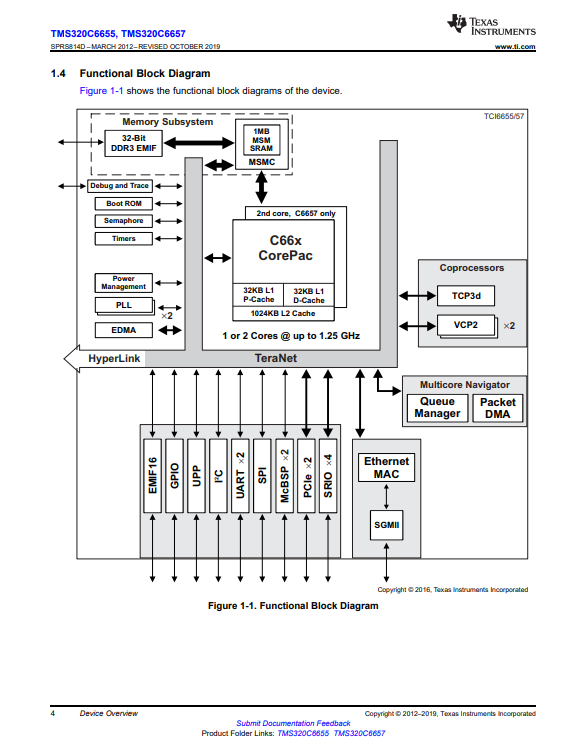

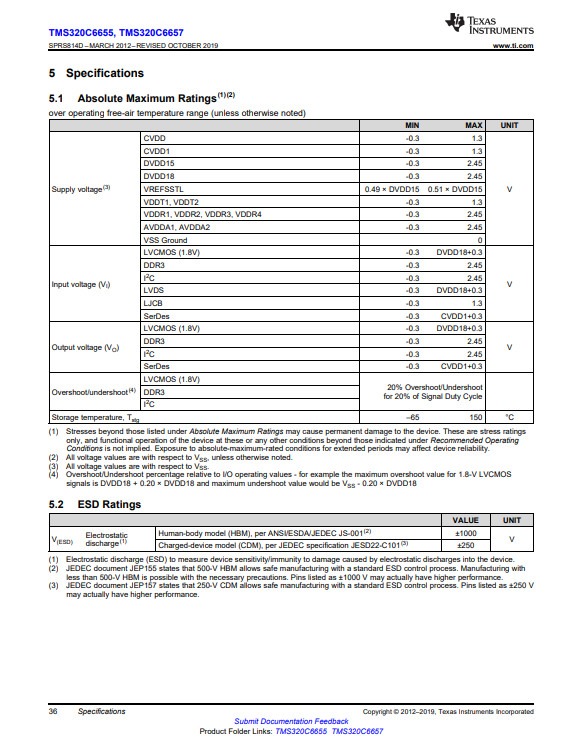

TI'S KeyStone architectura praebet programmabilem suggestum variis subsystematibus (C66x coros, memoria subsystem, periphericis et acceleratoribus) et utitur pluribus componentibus et technicis arteriis ad maximizandum intradevice et interdevice communicationis quae varias facultates DSP efficienter et compagem operatur.Integrae huic architecturae partes praecipuae sunt ut Multicore Navigator qui dat procurationem efficientis inter varias machinas compositas.TeraNet est inexplicabilis fabricae fabricae ut ieiunium et contentionem liberorum datorum internorum motus efficiat.Multicore communis memoria moderatoris aditum ad memoriam communem et externam permittit directe sine e facultate switch fabricae trahens.Pro usu puncto fixo, nucleus C66x habet 4× multiplicationem cumulandi (MAC) facultatem nucleorum C64x+.Praeterea, C66x nucleus integrat facultatem fluitantis et per- core rudis computationis effectus est industria ducens 40 GMACS per core et 20 GFLOPS per core (@1.25 GHz frequentiam operantem).Core C66x una cura fluitantis MAC operationes per cyclum praecisionem facere possunt et operationes duplices et mixtae praecisionem exercere possunt et est IEEE 754 obsecundans.Core C66x 90 novas instructiones (prae C64x+core) iaculis pro fluctuatione et vectore math processus ordinati.Hae amplificationes praebent amplitudines in nucleis popularibus DSP acinis adhibitis in insignibus processus, mathematicis, et imaginis acquisitionis functionibus.Core C66x est retrorsum codicem compatible cum C6000 praecedentis generationis TI fixum- et punctum DSP nuclei fluitantis, curans portabilitatem programmatum et cyclos programmandi abbreviati pro applicationibus ad hardware citius migrandi.C665x DSP magnam vim in-conditionis memoriam integrat.Praeter 32KB programmatis et notitiae cache, 1024KB memoriae dedicatae sicut praeformata RAM vel cella configurari possunt.Meditationes etiam 1024KB of Multicore Memoriae Communes integrant quae adhiberi possunt ut communis L2 SRAM et/vel L3 SRAM communicata.Omnes L2 memoriam erroris deprehensionis et erroris correctionis incorporamus.Ad accessum ad memoriam externam festinanter, haec fabrica includit 32 frenum DDR-3 interfaciem memoriam externam (EMIF) currentem ad 1333 MHz et firmamentum ECC DRAM habet.

| Formularium: | |

| attributum | Precium |

| Categoria | Integrated Circuitus (IC) |

| Embedded - DSP (Digital Processors signum) | |

| Mfr | Texas Instrumenta |

| Series | TMS320C66x |

| sarcina | Tray |

| Pars Status | Active |

| Type | Fixum / fluctuetur |

| Interface | DDR3, EBI/EMI, Aer, McBSP, Plu, I²C, SPI, UART, UPP |

| Horologium Rate | 1GHz |

| Memoria non volatilis | ROM (128kB) |

| On-Chip Ram | 2.06MB |

| Voltage - I/O | 1.0V, 1.5V, 1.8V |

| Voltage - Core | 1.00V |

| Operating Temperature | -40°C ~ 100°C (TC) |

| Adscendens Type | Superficie montis |

| Sarcina / Case | 625-BFBGA, FCBGA |

| Elit Fabrica Package | 625-FCBGA (21x21). |

| Basis Product Number | TMS320 |

RelatedPRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp