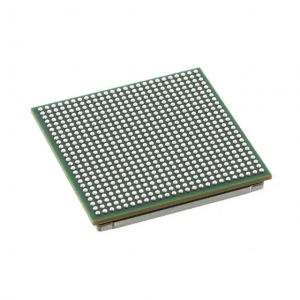

XCF128XFTG64C IC PROM SRL 128M PORTA 64-FTBGA

Product Parameter

Descriptio

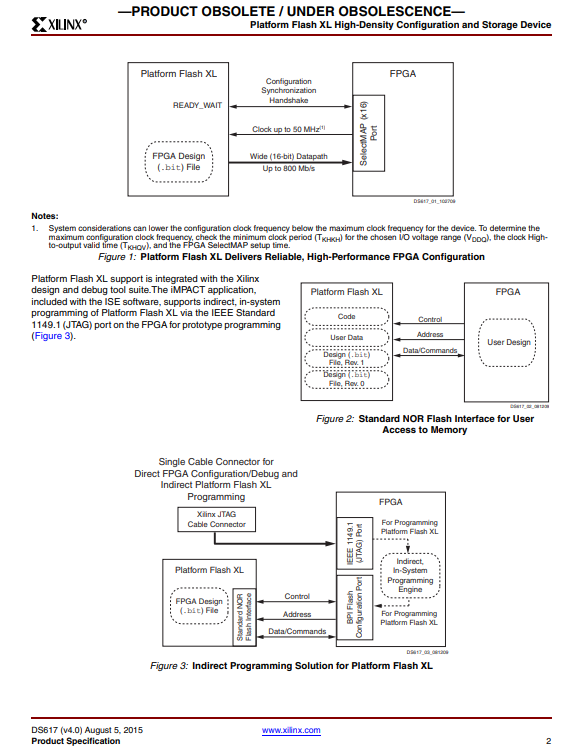

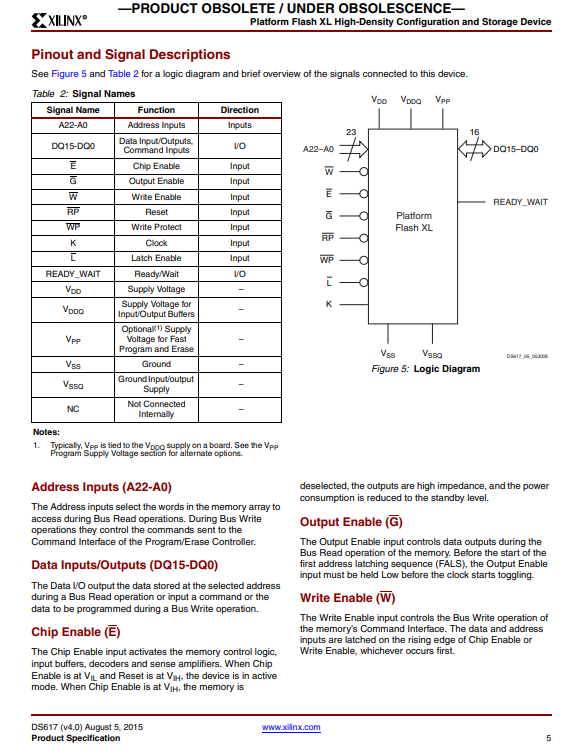

Certum foedus summus perficientur configurationem bitstrem repositionis ac solutionis partus essentialis est summus densitatis FPGAs.Rostra Flash XL est summa industria faciendo figuram et fabricam repositionis et maxime optimized pro FPGA configuratione summus effectus.Platform Flash XL integrat 128 Mb of in-system programmable mico repositionis et perficiendi notas pro configuratione intra sarcina parva vestigium FT64 (Figura 5).Potentia-in modum legitur rupta et dedicata I/O potentia copia fac rostris Flash XL ad compagem cum indigena SelectMAP conformationem interfaciem coire.A latum, 16 frenum notitiarum bus liberat FPGA configurationem bitstrem celeritatibus usque ad 800 Mb/s sine mora civitates.Vide UG438, Platform Flash XL Configuratio et Repono Fabrica User Guide, pro ratio-gradu usus et peractio consideratio.Rostra Flash XL ad usum Virtex-5 vel Virtex-6 FPGAs tantum sustentatur.Utere cum vetustioribus familiis Virtex, Spartan® familiis, vel AES rivulis encryptatis non sustinetur.Rostra Flash XL est solutio mico repositionis non volatilis, optimized pro configuratione FPGA.Consilium praebet READY_WAIT signum quod initium conformationis FPGA processuum conformat, et meliori certandi ratio et consilio tabulae simplicior est.Platform Flash XL potest excutere an XC5VLX330 bitstrem (79,704,832 bits) in minus quam 100 ms, efficiendi conformationem faciendam in rostris Flash XL idealis pro PCI expressis terminis et aliis applicationibus summus perficiendi.Rostra Flash XL est solutio conformationis unicae cum accessione systematis gradus facultatum.Vexillum NOR mico interface (Figura II) et subsidium communis mico interfaciei (CFI) quaesita industriam vexillum accessum ad spatium memoriae fabricae praebent.In rostris Flash XL's 128 Mb capacitas typice unam vel plures FPGA bitsulas continere potest.Quodlibet spatium memoriae non pro repositione bitstream adhibitum adhiberi potest ut notitia propositi generalis vel processus codici immergatur.

| Formularium: | |

| attributum | Precium |

| Categoria | Integrated Circuitus (IC) |

| Memoria - Configurationis Proms pro FPGAs | |

| Mfr | Xilinx Inc. |

| Series | - |

| sarcina | Tray |

| Pars Status | Active |

| Programmable Type | In Ratio Programmable |

| Memoria Location | 128Mb |

| Voltage - Supple | 1.7V ~ 2V |

| Operating Temperature | -40°C ~ 85°C |

| Adscendens Type | Superficie montis |

| Sarcina / Case | 64-TBGA |

| Elit Fabrica Package | 64-FTBGA (10x13) |

| Basis Product Number | XCF128 |

RelatedPRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp